International Research Journal in Global Engineering and Sciences. (IRJGES) ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 129-139 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

# ON CHIP DATA ENCODING FOR LOW POWER DISSIPATION

Revathy.A<sup>1</sup>, Indhumathi.G<sup>2</sup>, Dr.C.Rajalingam<sup>3</sup>, M.Evangelin Lydia<sup>4</sup>, T.Annie Sophia<sup>5</sup>

<sup>1</sup>Assistant Professor, Loyola Institute of Technology, Chennai-123, reva92ece@gmail.com

<sup>2</sup>Assistant Professor, Loyola Institute of Technology, Chennai-123, indhushine@gmail.com

<sup>3</sup>Associate Professor, Loyola Institute of Technology, Chennai-123.

<sup>4</sup>Assistant Professor, Loyola Institute of Technology, Chennai-123.

<sup>5</sup>Assistant Professor, Loyola Institute of Technology, Chennai-123.

Abstract: VLSI circuit design consuming low power become necessary for present technologies .one way of reducing dynamic power consumption in a CMOS circuit is to reduce the number of switching activity. In fact, self-switching and coupling switching activity is responsible for link power dissipation. The aim of low power data encoder is to transmit the data on the bus with reduced switching activity. In this paper the modified form of bus invert coding is implemented which is based on odd line and even line invert condition. Odd and even line condition is used to minimize the unwanted transitions on the data path which provides better results in terms of power dissipation and switching activity when compared to traditional businvert method

*Index Terms*—Bus-invert coding, self-switching activity, coupling switching activity, low power, data encoding, link power

### **I INTRODUCTION**

As semiconductor technology scales to nanometer technology, power consumption has been critical constraint in the design of digital systems due to widely used portable systems .Among the architectural components at the system level, buses that interconnect subsystems are important components, which consumes significant power. In VISI on-chip bus lines loaded with large capacitance. The amount of power dissipated by bus is directly proportional to the product of average number of logic transitions and bus capacitance. The better way of reducing power dissipation on bus is to encode the data with reduced switching activity. The rest of the paper is organized as follows. Power classification is discussed in section II, Switching activity is briefly discussed in section III, Related work is discussed in section IV, Proposed work is discussed in detail in section V, section VI and VII gives results and conclusion respectively.

ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 121-128 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

### **II POWER CLASSIFICATION**

The total power consumption in the VLSI chip comprises of dynamic power, short circuit power ,static power and leakage power .It can be simply described as summation of all these components.

$$p = \frac{1}{2c} v_{dd}^2 f N + Q_{SC} V_{dd}^2 f N + I_{leak} v_{dd}$$

#### Switching activity power

Switching activity power is the power required to charge and discharge circuit nodes .Node capacitance is represented by C. The factor N is the switching activity, i.e. the number of gate output transitions per clock cycle. In addition to voltage and physical capacitance, switching activity is the third factor that determines the dynamic power consumption. Only the switching activity contributes to dynamic power even though a chip contains high amount of physical capacitance.

#### Short circuit power

Power dissipation during occurs on output transitions due to current flowing from the supply voltage to the ground ,this is called as short-circuit current. The term Q\_SC represents the quantity of charge carried by the short-circuit current per transition.

#### Static power

Static power is also called as leakage power, leakage current which is primarily determined by the technology used in its construction, and consists of reverse bias current and sub-threshold current. In a MOS transistor bias current formed in the reverse direction in the parasitic nodes in between source and drain diffusions and the bulk region.Sub-threshold currents that arise from the inversion charges that exists at the gate voltages below the threshold voltage.

### **III SWITCHING ACTIVITY**

Switching activity can be classified into two types such as self-switching activity and coupling switching activity. Self-switching activity is defined as transitions on the capacitance between a bus line and the substrate (ground) while coupling transitions are defined as transitions on the capacitance between adjacent lines. Coupling transition in-between two adjacent links can be categorized as four types such as type-1, type-2, type-3 and type-4.Type-1 transition occurs if any one of the two lines changes state. Type-2 occurs if one wire switches from high to low and other switches from low to high.Type-3 occurs when both the line switches from low to high or high to low.Type-4 occurs when both line do not switch.

ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 121-128 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

### **IV RELATED WORK**

Some of the existing solutions to reduce the coupling switching activity are as follows, increasing line to line spacing and non-uniform wire placement is a method to decrease the physical coupling capacitance between buslines, busordering, busswizzling ,repeater staggering, skewing signal transition timing of adjacent lines and passive shielding is a well-known technique to reduce coupling effects is to insert static(ground or power) lines between bus data lines. This technique is known as passive shielding. Passive shielding eliminates the worst-case switching condition when two adjacent lines oppositely switch, resulting in a better worst-case delay. A good alternative to passive shielding is active shielding. In this method a shield is allowed to switch depending upon switching pattern of its adjacent bus lines. Among all these method data encoding provides better result. This method have to be modified to target a power cost function, namely, weighted switching activity. Intuitively, if a state S has a large number of transitions to state q, then the two states should be given uni-distant codes, so as to minimize switching activity at the flip-flop outputs.

### V PROPOSED WORK

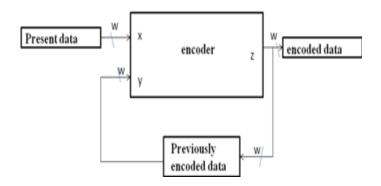

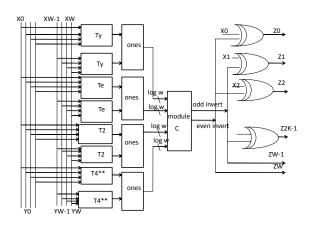

The basic idea of the proposed approach is encoding the data before transmitting on the link with the goal of minimizing the self-switching activity and the coupling switching activity in the links traversed by the data. For the proposed scheme, an encoder and a decoder block are added to the each intellectual property on the chip. The decoder just does the opposite work of the encoder block. The general encoder architecture is shown in Fig.1. the encoding logic changes according to the odd or even or full or no invert condition. Consider a link width of w bits. If no encoding is used, the incoming data is transmitted as it is via the link.

Fig.1. Encoder architecture

In this proposed work the incoming data is encoded according to encoding logic and transmitted via the link and the encoded data is decoded at the receiving end. In this approach one bit of the data is used for the inversion bit, which indicates if the data traversing the link has

ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 121-128 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

been inverted or not. w bits are the concatenation of w-1 payload bits and a "0"bit, represents the first input of the encoder ,while the previous encoded data represents the second input of the encoder. The decoder circuit simply inverts the received data when the inversion bit is high. The power model is described that contains different components of power dissipation of a link. The dynamic power dissipated by the interconnects and drivers is

$$P = [T_{0 \to 1}(C_S + C_l) + T_C C_C] V_{dd}^2 F_{ck}$$

(1)

Where  $T_{0 \rightarrow 1}$  is the number of  $0 \rightarrow 1$  transitions in the bus in two consecutive transmissions,  $T_c$  is the number of correlated switching between physically adjacent lines,  $C_s$  is the line to substrate capacitance,  $C_l$  is the load capacitance,  $C_c$  is the coupling capacitance,  $V_{dd}$  is the supply voltage, and  $F_{ck}$  is the clock frequency.

The effective switched capacitance varies from type to type, and hence, the coupling transition activity,  $T_c$ , is weighted sum of different types of coupling transition contribution. Therefore

$$T_c = K_1 T_1 + K_2 T_2 + K_3 T_3 + K_4 T_4 \tag{2}$$

Where  $T_i$  is the average number of type i transition and  $K_i$  is its corresponding weight According to [1]  $K_1 = 1, K_2 = 2$ , and  $K_3 = K_4 = 0$ . The occurrence probability of types I and II for a random set of data is 1/2 and 1/8, respectively. This leads to a higher value for  $K_1T_1$ compared with  $K_2T_2$  suggesting that minimizing the number of type I transition may lead to a considerable power reduction. Using (2),(1) may be expressed as

$$P = [T_{0 \to 1}(C_{s} + C_{l}) + (T_{1} + 2T_{2})C_{c}] V_{dd}^{2}F_{ck}$$

(3)

According to [2],  $C_l$  can be neglected

$$P \alpha T_{0 \to 1} C_{S} + (T_{1} + 2T_{2}) C_{c}$$

(4)

Occurrence probability for different types of transitions is calculated as follows; consider the data at time (t-1) and data at time (t) refer to the previous data and present data respectively. Considering only two adjacent bits of the physical channel. Sixteen different combinations of these four bits could occur (table I).Note that the first bit is the value of the generic ith line of the link, whereas the second bit represents the value of its (i+1)th line. The number of transitions for types I, II, III, and IV are 8,2,2,and 4,respectively.For a random set of data ,each of these sixteen transitions has the same probability for Type I,II,III,and IV are 1/2,1/8, 1/8, and 1/4,respectively.

<sup>132 |</sup> Revathy. A et.al. | www.irjges.com

ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 121-128 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

|      |                   | LITLC  |       | V LIGIOI           |         |       |

|------|-------------------|--------|-------|--------------------|---------|-------|

| Time | Normal            |        |       | Odd Inverted       |         |       |

|      | Туре І            |        |       | Type II,III and IV |         |       |

| t-1  | 00,11             | 00,11, | 01,10 | 00,11              | 00,11,  | 01,10 |

|      |                   | 01,10  |       |                    | 01,10   |       |

| t    | 10,01             | 01,10, | 11,00 | 11,00              | 00,11,  | 10,01 |

|      |                   | 00,11  |       |                    | 01,10   |       |

|      | T1*               | T1**   | T1*** | Туре               | Type IV | Туре  |

|      |                   |        |       | III                |         | II    |

|      | Туре ІІ           |        |       | Туре І             |         |       |

| t-1  | 01,10             |        |       | 01,10              |         |       |

| t    | 10,01<br>Type III |        |       | 11,00              |         |       |

|      |                   |        |       | Туре І             |         |       |

| t-1  | 00,11             |        |       | 00,11              |         |       |

| t    | 11,00             |        |       | 10,01              |         |       |

|      | Type IV           |        |       | Туре І             |         |       |

| t-1  | 00,11,01,10       |        |       | 00,11,01,10        |         |       |

| t    | 00,11,01,10       |        |       | 01,10,00,11        |         |       |

### TABLE I EFFECT OF ODD INVERSION

TABLE IIEFFECT OF EVEN INVERSION

|      |                   |        |       | 1 Engloit |                    |       |  |  |

|------|-------------------|--------|-------|-----------|--------------------|-------|--|--|

| Time | Normal            |        |       |           | Even Inverted      |       |  |  |

|      | Туре І            |        |       |           | Type II,III and IV |       |  |  |

| t-1  | 01,10             | 00,11, | 00,11 | 01,10     | 00,11,             | 00,11 |  |  |

|      |                   | 01,10  |       |           | 01,10              |       |  |  |

| t    | 00,11             | 10,01, | 01,10 | 10,01     | 00,11,             | 11,00 |  |  |

|      |                   | 11,00  |       |           | 01,10              |       |  |  |

|      | T1*               | T1**   | T1*** | Туре      | Type IV            | Туре  |  |  |

|      |                   |        |       | III       |                    | II    |  |  |

|      | Type II           |        |       |           | Туре І             |       |  |  |

| t-1  | 01,10             |        |       |           | 01,10              |       |  |  |

| t    | 10,01<br>Type III |        |       |           | 00,11              |       |  |  |

|      |                   |        |       |           | Туре І             |       |  |  |

| t-1  | 00,11             |        |       |           | 00,11              |       |  |  |

| t    | 11,00<br>Type IV  |        |       |           | 01,10              |       |  |  |

|      |                   |        |       |           | Туре І             |       |  |  |

| t-1  | 00,11,01,10       |        |       |           | 00,11,01,10        |       |  |  |

| t    | 00,11,01,10       |        |       |           | 10,01,11,00        |       |  |  |

ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 121-128 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

Data's in table is organized as follows .The first bit is the value of generic ith line of the link , whereas the second bit represents the value of its (i+1)th line. For each partition, the first(second)line represents the value at time t-1(t)

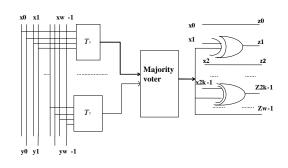

### A.ODD LINE ENCODER

Odd line encoder focus on reducing the number of Type I transitions(by converting them to types III and IV transitions) and type II transitions (by converting them to type I transitions). This method compares the current data with previous data to decide whether odd inversion or no inversion of the current data can lead to the link power reduction. Table I reports, for each transition, the relation-ship between the coupling transition activities of the data when transmitted as is and when its bits are odd inverted. As table I shows, if the data is odd inverted, Types II, III, and IV transitions convert to type I transitions. In case of type I transitions, the inversion leads to one of types II, III or IV transitions. In particular, the transition indicated as  $T_1^*, T_1^{**}$ , and  $T_1^{***}$  respectively.

Assuming link width of w bits, the total transitions between adjacent lines is w-1, and hence  $T_{y}$ 2

(5)

$$= (W - 1)/$$

In the Fig.2. the w-1 bits of the incoming(previous encoded) data are indicated by  $X_i(Y_i)$ , i=0,1,...w-2. The wth bit of the previously encoded data is indicated by inv which shows if it was inverted (inv=1)or left as it was(inv=0). In the encoding logic ,each  $T_{v}$  block takes the two adjacent bits of the input data (e.g.,  $x_1x_2y_1y_2$ ,  $x_2x_3y_2y_3$ ,  $x_3x_4y_3y_4$ , ) and sets its output to "1" if any of the transition types of  $T_y$  is detected. This means that the odd inverting for this pair of bits leads to the reduction of the link power dissipation (table I). The  $T_y$  block may be implemented using a simple circuit. The second stage of the encoder, which is a majority voter block, determines if the condition (5) is satisfied (a higher number of 1s in the input of the block compared to 0s). if this condition is satisfied, in the last stage, the inversion is performed on odd bits. Thus the working principle of simple odd line encoder.

<sup>134 |</sup> Revathy. A et.al. | www.irjges.com

ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 121-128 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

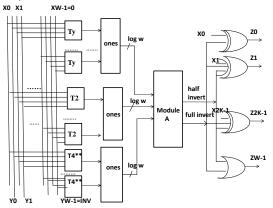

### B. ODD/FULL LINE ENCODER

This method makes use of both odd and full inversion. The full inversion operation converts Type II transitions to Type IV transitions. This encoding logic compares the current data with the previous one to decide whether the odd, full, or no inversion of the current data can give rise to link power reduction. The full inversion condition is obtained as,

$T_2 > T_4^{**}$  (6) where  $T_4^{**}$  is the transition from type II to IV. The operating principle of odd/full line encoder are similar to those of odd line encoder. The proposed encoding architecture is based on odd invert condition (5) and the full invert condition(6) is shown in Fig.3. Here again ,the wth bit of the previously and the full invert condition of(6) is show in Fig.3. Here again ,the wth bit of the previously encoded body flit is indicated with inv which defines if it was odd or full inverted (inv=1)or left as it was (inv=0).

In this encoder, in addition to the  $T_{Y}$  block in odd line encoder, the  $T_{2}$  and  $T_{4}^{**}$  blocks which determine if the inversion based on the transition types  $T_{2}$  and  $T_{4}^{**}$  should be taken place for the link power reduction. The second stage is formed by a set of 1s blocks which count the number of 1s in their inputs. The output of these blocks has the width of  $log_{2}w$ . The output of the top 1s block determines the number of transitions that odd inverting of pair bits leads to the link power reduction. The middle 1s block specifies the number of transitions that full inverting of pair bits leads to the link power reduction. Finally the bottom 1s block specifies the number of transitions whose full inverting of pair bits leads to the increased link power. Based on the number of 1s for each transition type, Module A decides if an odd invert or full invert action should be performed for the power reduction. For this module if (5) or (6) is satisfied, the corresponding output signal will become "1".In case no invert action should be taken place, none of the output is set to "1", Module A can be implemented using full-adder and comparator blocks.

ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 121-128 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

### C. ODD/FULL/EVEN LINE ENCODER

In this method even inversion is added .The reason is that odd inversion converts some of type I  $(T_1^{***})$  transitions .As can be observed from Table II ,if the data even inverted ,the transitions indicated as  $T_1^{**}/T_1^{***}$  in the table are converted to type IV/type III transitions .Therefore ,the even inversion may reduce the link power dissipation as well. This method compares the current data with the previous data to decide whether odd, even, full, or no inversion of the current data can give rise to the link power reduction.

Fig.4. Odd/even/full line encoder

(8)

The even invert condition is given as

$T_{e} > (w-1)/2, T_{e} > T_{y}, 2(T_{2} - T_{4}^{**}) < 2T_{e} - w+1$  (7)

The full inversion condition is obtained as  $2(T_2 - T_4^{**}) > 2T_e$ -w+1

Then the condition for odd invert condition is given by  $2(T_2 - T_4^{**}) < 2T_y - w + 1, \quad T_y > (w - 1)/2, T_e < T_y$  (9)

When none of (7),(8).(9) is satisfied, no inversion will be performed. The operating principle of this encoder is similar to those of the encoders implementing odd line and odd/full line encoder. The proposed encoding architecture, which is based on the even invert condition of (7), the full invert condition (8) and the odd invert condition (9) is show in Fig.4.The wth bit of the

ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 121-128 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

previously encoded data is indicated by inv which shows if it was even, odd or full inverted (inv=1)or left as it was(inv=0). The first stage of the encoder determines the transition type while the second stage is formed by a set of 1s blocks which count the number of ones in their inputs. In the first stage, the  $T_e$  block is added which determines if any of the transition types of  $T_2$ ,  $T_1^{**}$ ,  $T_1^{***}$  is detected for each pair bits of their inputs. For these transition types, the even invert action yields link power reduction. Again .four ones block is added to determine the number of detected transition for each  $T_y$ ,  $T_e$ ,  $T_2$ ,  $T_4^{**}$ , blocks. The output of the ones block is input for Module C. This module determines if odd, even, full, no invert action corresponding to the outputs "10," "01,""11," or "00,"respectively, should be performed. The outputs "01," "11,"and "10" show that whether (7), (8), (9), respectively, are satisfied. The Module C was designed based on the condition given in (7),(8),(9).

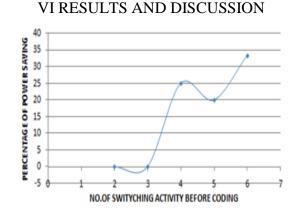

Fig.5. odd line encoder performance graph

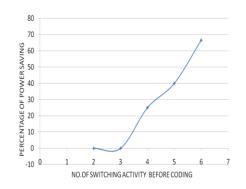

Fig.6 odd/full line encoder performance graph

ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 121-128 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

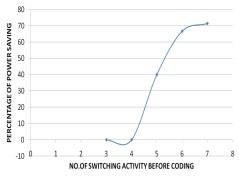

Fig.7. odd/full/even line encoder

From the performance graph it can be observed that the average power saving of odd line encoder is 20.6%, the average power saving of odd/full line encoder is 35.8% and the average power saving of odd/even/full line encoder is 88.12%. All these encoding approach add overhead in terms of power consuming by any integrated circuit incorporating the proposed encoder and also incurs area overhead on the chip, still it acquires the routing delay of data but still the power saving by the encoding logic gives better results in terms of power dissipation by reducing the coupling switching activity.

### VII CONCLUSION

Since the technology moving towards DSM to VDSM, technology the bus encoding has to overcome present scenario. The proposed data encoding technique called odd/even/full line encoder significantly reduces power dissipated by the links of a chip which accounts significant fraction of the total power budget. The performance of the encoder is evaluated in terms of switching activity and power saving.

### REFERENCES

- [1] K. W. Ki, B. Kwang Hyun, N. Shanbhag, C. L. Liu, and K. M. Sung, "Coupling-driven signal encoding scheme for low-power interfacedesign," in Proc. IEEE/ACM Int. Conf. Comput.-Aided Design, Nov. 2000, pp. 318–321.

- [2] w.wolf,A.A.Jerraya,and Martin,"multiprocessor system-on-chip MPSOC technology,"comput-Aided Design IntegrCcircuits Syst.,vol.27,no.10,pp.1701-1713.oct.2008.

- [3] L.Benini and G.De Micheli." Networks on chip:A newSOC paradigm,"Computer,vol.35,no.1,pp.

78,jan.2002.D.Yeh,L.S.Peh,S.Borkar,J.Darringer,A.Agarwal,and W.M.Hwu,"Thousand-core chips roundtable,"IEEE Design Test comput.,vol.25,no.3,pp.272-278,May-Jun.2008.

ISSN : 2456-172X | Vol. 3, No. 1, March - May, 2018 Pages 121-128 | Cosmos Impact Factor (Germany): 5.195 Received: 23.03.2018 Published : 22.04.2018

- [4] A.Vittal and M. Marek-Sadowska, "Crosstalkreduction for VLSI,"IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 16, no. 3,pp. 290–298, Mar. 1997.

- [5] M. Ghoneima, Y. I. Ismail, M. M. Khellah, J. W. Tschanz, and V. De, "Formal derivation of optimal active shielding for low-power on-chip buses," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 25,no. 5, pp. 821–836, May 2006.

- [6] K. Banerjee and A. Mehrotra, "A power-optimal repeater insertion methodology for global interconnects in nanometer designs," IEEE Trans. Electron Devices, vol. 49, no. 11, pp. 2001–2007, Nov. 2002.

- [7] M. R. Stan and W. P. Burleson, "Bus-invert coding for low-power I/O," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 3, no. 1,pp. 49–58, Mar. 1995.

- [8] S. Ramprasad, N. R. Shanbhag, and I. N. Hajj, "A coding framework for low-power address and data busses," IEEE Trans. Very Large ScaleIntegr. (VLSI) Syst., vol. 7, no. 2, pp. 212–221, Jun. 1999.

- [9] C. L. Su, C. Y. Tsui, and A. M. Despain, "Saving power in the control path of embedded processors," IEEE Design Test Comput., vol. 11, no. 4, pp. 24–31, Oct.–Dec. 1994.

- [10] L. Benini, G. De Micheli, E. Macii, D. Sciuto, and C. Silvano, "Asymptotic zerotransition activity encoding for address busses in low-powermicroprocessor-based systems," in Proc. 7th Great Lakes Symp. VLSI Mar. 1997,

- [11] L.Benini, A.Macii, M.Zoncino, and R.Scarsi "Architectures and synthesis algorithms for power-efficient bus interfaces," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 19, no. 9, pp. 969–980, Sep. 2000.